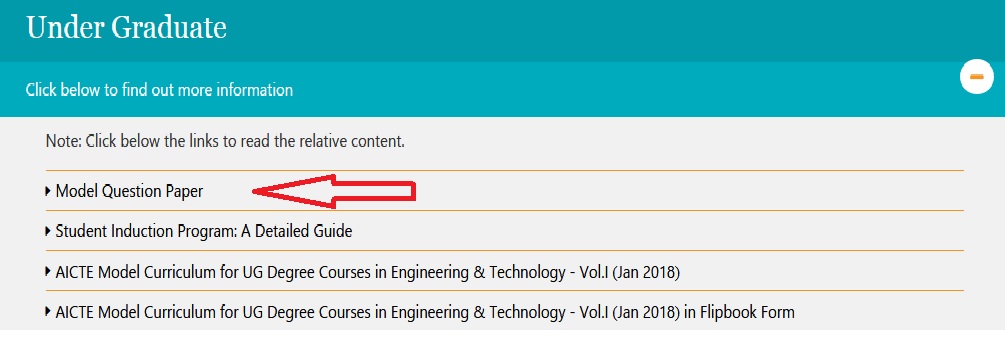

AICTE Electronics & Communications Engineering UG Model Question Papers : All India Council for Technical Education

Name of the Instution : All India Council for Technical Education

Class : Undergraduate Programs – UG

Document Type : Model Question Papers

Paper : Electronics & Communications Engineering

Year : 2018

Website : https://www.aicte-india.org/education/model-syllabus

AICTE ECE UG Model Question Papers

Download Civil Engineering Model Question Papers For Undergraduate Program from the All India Council for Technical Education website. The model question papers are suggestive blueprints.

Related : AICTE Electrical & Electronics Engineering UG Model Question Papers : www.pdfquestion.in/33536.html

The primary aim of these question papers is to bring clarity about the process of connecting questions to performance indicators and hence to course outcomes.

Analog Electronics Circuits

1a Design the following circuit to provide the output voltage V0 of 3.8V. Assume that the diodes have 0.7V drop at 1mA and ?V=0.1V/decade change in current.

1b Derive the DC bias currents IB, IC, IE, VCE and SICO for voltage divider biasing using BJT. Draw the DC load line and locate the operating point. With the help of sequence of events show how the operating point is stabilized.

1c Design a circuit using suitable components to obtain the following input- output characteristics and explain the working of the same.

2a The input voltage Vi to the circuit shown below varies linearly from 0 to 150V. Sketch the output waveform. Assume diodes as ideal.

2b List different diode models. Explain any three models in detail. 7 1 2 1.4.2

2c Identify the circuit and plot the output waveform if the input signal Vi shown below is applied. Given C=1µF, V= 5V, cut in voltage of the diode V?=0.7V

3a Identify the following amplifier configuration and determine the DC bias voltages and currents to locate the Q-point. Compute various amplifier parameters when R1=68kO, R2=12kO, VCC=18V, RC=2.2kO, RE=1.2kO, hfe=180, hie=2.75KO, hoe=25µmho.

3b Prove that rd = nVT/ID for a small signal diode model with necessary circuit diagram and transfer characteristics curve.

3c Draw the steady state output waveform for the following circuit indicating maximum and minimum value of the output. Given Rr=2MO, Rf=0O cut-in voltage of diode = 0V, input voltage is 5KHz square wave varying between +10V and -10V.

4a Find the values of circuit elements shown below for given current ID of 0.4mA, VD=0.5V, Vt=0.7V, µnCox= 100mA/V2, L=1µm & W=32µm VDD=-VSS=2.5V. Neglect channel length modulation effect.

Download ECE Question Paper :

https://www.pdfquestion.in/uploads/pdf2019/33542-ECE.pdf

4b Design the circuit elements as shown in below figure to establish a DC drain current of 0.5mA. The NMOS is specified to have Vt=1V and kn’(W/L)=1mA/V2 and ?=0. Calculate the percentage change in the value of ID obtained when the MOSFET is replaced with another MOSFET having same kn’(W/L) but Vt=1.5V

4c Draw the DC equivalent, AC equivalent and small signal equivalent model for common gate amplifier and derive the expressions for input, output impedance and voltage gain.

5a Derive an expression for drain current ID for NMOS in different regions of operation.

5b Consider common source amplifier with constant current source biasing technique where VDD= -VSS =15V, current I=0.5mA, RG=4.7MO, RD=10KO, Vt=1.5V and Kn’(W/L)=1mA/V2. Determine the Q-points and all the amplifier parameters assuming VA=75V.

5c Using two transistors Q1 and Q2 having equal lengths but different widths related by W2/W1 = 5. Design a circuit that replicates current and obtain I=0.5mA. Let VDD=5V, kn’(W/L)1= 0.8mA/V2, Vt=1V and ?=0. Find the required value of R? What is voltage at the gates of Q1 and Q2? What is the lowest voltage allowed at the drain of Q2 while Q2 remains in the saturation region?

Automotive Electronics

1a The vehicle is to be started on a cold winter morning, and then has to navigate hilly terrains. How does the engine cope-up with the different requirements as the vehicle goes from start to cruising? Suggest a design strategy using different control modes with appropriate details.

1b What is Stoichiometric ratio?

i) Calculate Lambda if air fuel ratio is 13.2.

ii) Determine the fuel injector pulse duration (base pulse width Tw) and fuel quantity for the eight cylinder fully warmed up and very cold engine running at 4000 rpm, having a fuel flow rate of 0.0022Kg/sec and mass air flow rate of 0.0035Kg/sec.

1c For the development of an Engine ECU, apply MBD approach adhering to automotive V design model.

2a With MAF sensor malfunctioning as detected by the engine control system diagnostic function, how engine control system can work effectively as possible with other existing sensor information for calculating the mass air flow rate.

2b Assume a vehicle is running at a fixed rpm of 8000 and further the driver demands for increase in speed. How the engine ECU handles driver’s request using ignition timing? Suggest a suitable Instrumentation system with related electronics for closed loop control of ignition timing.

2c Vehicle is moving with a high speed; suddenly the driver applies the brakes, what is the physical consequence of this condition on wet and dry surface? Provide a suitable control system/electronic solution to avoid the damage.

3a What do you mean by Engine Mapping? For the engine operating in closed loop mode how the variations in,

i) Exhaust gas recirculation

ii) Air fuel ratio and

iii) Ignition timing affect its performance. Show with the necessary plots.

3b Elaborate on different segments of automotive industry and also discuss about automotive supply and value chain.

3c Vehicle is moving on an icy surface with the engine rpm of 4000, but the vehicle is unable to move forward, what is the physical consequence of this condition? Provide a control system solution to overcome this problem.

CMOS VLSI Circuits

1a Analyze the impact of Semi-custom and Full-custom VLSI design styles based on design cycle time and the achievable circuit performance.

1b What are the limitations of planar VLSI technology, and discuss the advantages and challenges in 3D devices like FinFET devices.

1c In VLSI fabrication, oxides in varying thickness and compositions are used for different processes. Discuss each of them with relevant examples.

2a Discuss the capacitance modeling of an nMOS device during cutoff, linear and saturation.

2b Design an AOI221 gate using fully CMOS logic, so as to achieve same transient performance as that of a reference CMOS Inverter.

3a An inverter needs to be fabricated using planar CMOS technology in a twin-tub process. Illustrate the fabrication steps with cross-sectional views andappropriate masks used at each stage.

4a Discuss the charge sharing issue in Dynamic CMOS logic. What will happen if we directly cascade two stages of this gate? Propose a remedy for the cascading problem.

4b In the figure, find the output in terms of inputs A, B and C when the clock CK is high. Also implement the clocked CMOS equivalent of the same.

Digital Circuits

1a Explain the working of ECL OR gate with the help of neat circuit diagram. 5 1 2 1.4.2

1b Rewrite the following Boolean expression in the minterm and maxterm canonical forms. P=F(x,y,z) =x’(y’+z)+z’

1c Design a digital circuit using minterm and maxterm generators to realize the following functionality. F(A,B,C,D) = m(0,1,3,4, 9,10,11,15). Use only 2- input gates.

2a On a certain weekend Ramu, Raheem and Johnny planned to have lunch in a restaurant and/or watch a movie.

i) When all friends agree, they will have lunch after watching a movie.

ii) No question of going out when none of them agree.

iii) If Ramu agrees, then irrespective of others opinion, they only have lunch together.

iv) If Ramu disagrees, they will only watch a movie. Design a suitable digital system by using a positive logic, for the above conditions with a non programmable technique in SOP and POS formats.

2b Realize the following Boolean function with multiplexer

F(A,B,C,D) = m(0,1,3,4,8,9,15)

i) Using 16:1 MUX

ii) Using 8:1 MUX with A,B,C select lines

iii) Using 4:1 MUX with A,B select lines

3a Identify a technique that cannot be programmed and that is used for less number of variables, to provide minimal sums and minimal products for the following Boolean function. f(w,x,y,z)= Sm( 1,5,8,14) + X( 4,6,9,11,15)

3b Design a digital system to add two Binary Coded Decimal numbers using binary adder.

4a Explain the operation of a SR latch. 7 3 2 1.4.2

4b Design a 4-bit Johnson counter using the principle of Universal Shift Register (USR)

4c The figure shows a binary up counter with synchronous clear input. With the decoding logic shown, the counter works as a Mod-n counter. Find the value of n.

Linear Integrated Circuits

1a Derive the expression for output impedance of Wilson current mirror with relevant circuit diagram and equivalent circuits.

1b For the non inverting amplifier R1=470O and RF=4.7K O, A=200000, Ri=2M O, Ro=75 Fo=5Hz, supply voltage is +/-15V and output voltage swing is +/-13V .Calculate the values of AF, Rif. Rof ,Ff and VOOT

1c Consider the circuit shown below, assuming (W/L)1-3=40/0.5,Iref=0.3mA

a. Determine Vb such that Vx=Vy

b. If Vb deviates from the value calculated in part (a) by 100mV, what is the mismatch between Iout and Iref?

2a Derive an output voltage expression for 5-pack differential amplifier with neat circuit diagram with relevant Explanation.

2b Discuss the effect of negative feedback on non-idealities of the Op-amp, with neat diagram and relevant equations.

2c Identify the circuit shown below where all transistors have Vt=0,6V, µnCox=160 W1=W4=4µm, and W2=W3=40µm. L=1µm and IREF is 20µA. Determine the

output current and the voltages at the gates of Q2 and Q3. What is the lowest voltage at the output for which current source operation is possible? What are the values of gm and ro of Q2 and Q3? What is the output resistance of the circuit?

3a Identify the amplifier configuration given below, with (W/L)1,2=25/0.5, µnCox=50µA/V2, VTH=0.6V, ?=?=0 and VDD =3V

a. What is the required input CM for which RSS sustains 0.5V?

b. Calculate RD for a differential gain of 5

3b List the ideal characteristics of an OPAMP. Give its symbolical representation and explain the functions of each terminal. Tabulate the ideal op-amp terminal characteristics.

3c For the differential amplifier with the current mirror as a load ,determine the (W/L) and drain current of all MOSFET’s for the following specifications: Vdd=-Vss=2.5V,SR>=10V/us (Cload=5pf),f-3db>= 100kHz (CL=5pF),a small signal voltage gain of 100,-1.5<=ICMR<=2V and Pdiss<=1mW. Model arameters: KN’= 110uA/V2, KP’= 50uA/V2, VTP=-0.7V, VTN=0.7V, ?N=0.04V- 1,?P= 0.05V-1.

Operating System & Embedded Systems

1a Calculate the average wait time & TAT for following processes using

• SJF (pre-emptive & non-pre-emptive),

• Priority scheduling

• RR

1b i. Apply suitable code optimization techniques for the following C statements.

ii. Determine the longest path through each code fragment, assuming that all statements can be executed in equal time and that all branch directions are equally probable.

1c Suppose computer system hardware is to be operated without an OS, discuss the scenario of using this computer for running an application in which password authentication is to be made. Discuss disadvantages of a computer without an OS. Elaborate on the role of OS and its functions.

2a Under what circumstances is rate-monotonic scheduling inferior to earliestdeadline- first scheduling in meeting the deadlines associated with processes? Consider the following activities of a car control system.

1. C= worst case execution time

2. T= (sampling) period

3. D= deadline

Speed measurement: C=4ms, T=20ms, D=20ms

ABS control: C=10ms,T=40ms, D=40ms

Fuel injection: C=40ms,T=80ms, D=80ms Try any of the two methods to schedule the tasks.

2b In a multiprogramming and time sharing environment, several users share the system simultaneously. Discuss the security problems that may arise in the situation. Assess the degree of security that can be achieved in both the cases.

2c It is required to generate a student’s register enrolled for engineering course in alphabetical order to distribute student’s ID. Develop a code using

i. Inline assembly

ii. Mixed assembly

comment on the performance w.r.t time and memory using appropriate optimization technique

3a Convert the algorithm given in flowchart into

1) “Normal” assembler, where only branches can be conditional.

2) ARM assembler, where all instructions are conditional.

3) Develop ‘C’ code with optimization

4) Comment on performance w.r.t 1, 2 and 3

3b Construct a simple “for loop” in C which operates on an array element in each iteration. Then rewrite the code using suitable loop optimization techniques. Comment on the performance.

3c An Operating system’s PID manager is responsible for managing process identifiers. A unique ID is assigned to the process when it is first created. Discuss how this PID is managed using PCB. Elaborate on process and PCB.